De regeling ‘Kenniswerkers’ van SenterNovem heeft het onderzoeksvoorstel van Bruco BV en het FOM-instituut voor subatomaire fysica Nikhef gehonoreerd. Twee kenniswerkers van Bruco zullen voor een periode van 18 maanden bij Nikhef werken aan twee projecten voor innovatieve uitleesstrategieën voor hybride pixeldetectoren.

Dit voorstel is één van de veertig gehonoreerde voorstellen die samen een subsidie van in totaal 100 miljoen euro krijgen. Bruco BV uit Borne ontwerpt en begeleidt de productie van geïntegreerde circuits (ASIC’s). Nikhef houdt zich bezig met verschillende projecten om de vergaarde kennis bij het ontwikkelen van detectoren in de subatomaire fysica ten goede te brengen van de maatschappij. Combinatie van deze expertise verbetert de huidige uitleestechniek door de uitlezing van de detectoren te versnellen en de opslagcapaciteit efficiënter te gebruiken. Met deze detachering kan hier een snelle en efficiënte start mee gemaakt worden.

Andere toepassingen

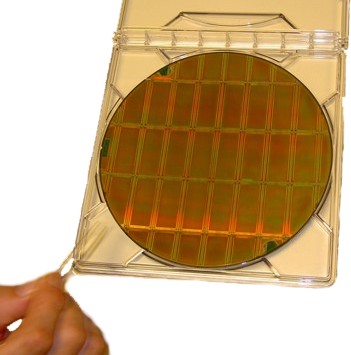

Hybride pixeldetectoren, oorspronkelijk ontwikkeld voor experimenten in de hoge-energie fysica, vinden in toenemende mate hun weg naar andere toepassingen, bijvoorbeeld in materiaalanalyse met röntgendiffractie en röntgenfluorescentie, maar ook in biomedische toepassingen en bij farmacologisch onderzoek zoals proteïne structuurbepalingen. Extreme verkleining in de nano-elektronica en driedimensionale stapeling van chips maken het mogelijk om steeds meer informatie te ontlenen aan steeds minder röntgenfotonen, door van ieder foton niet alleen de plaats van inval te bepalen, maar ook zijn golflengte en zijn aankomsttijd. Ook het gevoelig oppervlak en het aantal beelden dat per seconde kan worden geregistreerd, neemt sterk toe.

Door al deze ontwikkelingen explodeert de bandbreedte die nodig is om de nieuwste generatie van hybride pixeldetectoren uit te lezen. Binnen dit project worden enerzijds technieken ontwikkeld om via moderne seriële protocollen, zoals 10 gigabit ethernet, data sneller uit de uitlees-chip te halen, en anderzijds technieken om de hoeveelheid databits al op de chip te verminderen zonder de inhoud aan te tasten. Hierbij gaat het om On-Chip Sparse-data-Scan en On-Chip Data-Compression. De te ontwikkelen circuits zullen in de vorm van IP-blocks kunnen worden ingezet bij het ontwerp van de komende generaties pixel-readout chips.