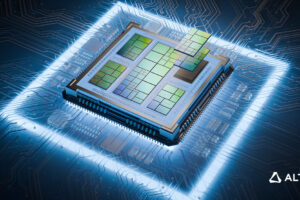

Een chip die zichzelf test en zo nodig repareert. Dit wordt mogelijk dankzij ontwikkelingen van onderzoekers van het Europese CRISP-consortium, met daarin onder meer het UT-instituut CTIT en spinoff Recore Systems. Miniaturisering maakt componenten en verbindingen op een chip in de toekomst steeds kwetsbaarder: een zelfreparerende chip is hierop voorbereid. Terwijl de chip gewoon aan het werk blijft, worden eventuele niet-werkende componenten opgespoord en wordt zo nodig een ‘omleidingsroute’ gekozen.

De keerzijde van de miniaturisering van chips is dat ze tegen hun fysieke limieten aanlopen: het wordt steeds lastiger om een goede opbrengst te halen bij de productie, en eenmaal geproduceerde chips zijn gevoeliger voor ‘breakdown’. "Omdat we steeds meer transistoren op een klein chipoppervlak concentreren, wordt het een echte uitdaging om de betrouwbaarheid van het uiteindelijke systeem te garanderen", zegt dr.ir. Hans Kerkhoff, specialist in ‘testable design and testing’ bij het Centrum voor Telematica en Informatietechnologie (CTIT) van de UT.

Tegels

Om de betrouwbaarheid van toekomstige generaties chips, ondanks die groeiende kwetsbaarheid, juist te vergróten, heeft het Europese CRISP-consortium, met vier bedrijven en twee universiteiten, onderzocht hoe chips zichzelf kunnen testen en repareren. Zo’n nieuwe chip is in staat te testen of er componenten of verbindingen zijn die niet werken, en zoekt dan naar alternatieve ‘paden’ om de benodigde functie toch uit te voeren met goed werkende componenten en verbindingen. Dat is mogelijk dankzij een modulaire opbouw, met vele ‘cores’ of tegels. Een run-time resource manager verdeelt daarbij de taken over de verschillende cores van de chip.

Maar hoe kan een chip voor de volle honderd procent functioneren, terwijl er niet-werkende componenten op zitten? "Je kunt natuurlijk proberen chips te ontwerpen die nooit in kwaliteit achteruitgaan. Maar die garantie krijg je niet.", zegt Kerkhoff. "Je kunt ook architecturen ontwikkelen die volledig blijven functioneren ondanks degradatie. ‘Graceful degradation’ noemen we dat ook wel. Een chip met vele ‘cores’, met goed ontworpen verbindingen ertussen, is dan een oplossing." De vele cores waaruit de chip bestaat, voeren ieder een subtaak uit voor een complexe toepassing: voor satellietnavigatie zijn bijvoorbeeld veel van dit soort subtaken nodig om alle digitale signalen te verwerken. De run-time resource manager bepaalt op een dynamische manier welke taak wordt toegewezen aan welke core. Omdat niet uitmaakt welke core een basistaak uitvoert – ze zijn inwisselbaar -, kan een goede core ook een taak overnemen van een falende. Zo kan de chip langere tijd betrouwbaar zijn werk blijven doen.

Bart Vermeulen, Senior Principal Scientist bij NXP Semiconductors: "De test op foute componenten, in combinatie met de run-time resource manager, vormt het hart van een flexibele herconfigureerbare chip, die in staat is veranderende taken en fouten het hoofd te bieden tijdens zijn hele levensduur. De resource manager houdt ook in de gaten dat de Quality of Service op peil blijft."

Over CRISP

Het project CRISP (Cutting edge Reconfigurable ICs for Stream Processing) onderzoekt herconfigureerbare ‘many-core‘ chips voor veeleisende ‘streaming’ toepassingen: hoe zijn deze chips efficiënt en betrouwbaar in te zetten en te programmeren? Doel van het project is een herconfigureerbare chip die voor talloze toepassingen bruikbaar is: van consumenten elektronica met lage kosten tot aan zeer veeleisende specialistische apparatuur. Het projectconsortium wordt geleid door Recore Systems, een succesvol spinoff bedrijf van het CTIT. Verdere projectpartners zijn de Universiteit Twente (CTIT), Atmel Automotive, Thales Nederland, Tampere University of Technology en NXP Semiconductors.