Niemand weet wat 2021 gaat brengen, maar Intel doet alvast zijn best om de voorspellingen van oprichter Gordon Moore te blijven waarmaken. Het bedrijf heeft een proces ontwikkeld waarmee twee transistors bovenop elkaar kunnen worden geplaatst.

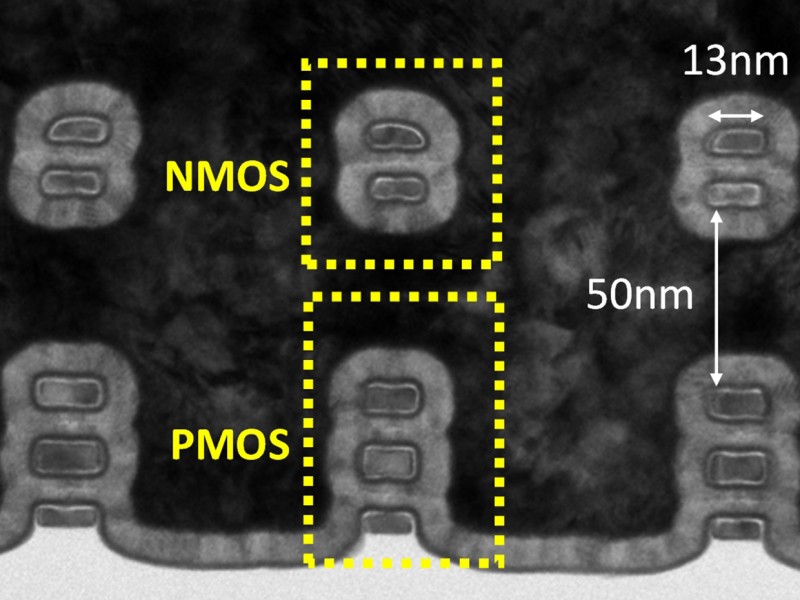

De logische schakelingen achter vrijwel elk digitaal apparaat zijn tegenwoordig afhankelijk van een koppeling van twee soorten transistors: NMOS en PMOS. Hetzelfde spanningssignaal dat een van hen inschakelt, schakelt de andere uit. Als je hun samenvoegt zou elektriciteit alleen moeten stromen wanneer een bit verandert, wat het stroomgebruik enorm zou moeten terugbrengen.

Het paar zit al tientallen jaren naast elkaar, maar als circuits moeten blijven krimpen, zullen ze toch nog iets dichterbij elkaar moeten kruipen. Tijdens de IEEE International Electron Devices Meeting (IEDM) liet Intel zien hoe het ze bij elkaar op schoot wil zetten. Het schema halveert de voetafdruk van een eenvoudig CMOS-circuit, wat een mogelijke verdubbeling van de transistordichtheid op toekomstige IC’s betekent.

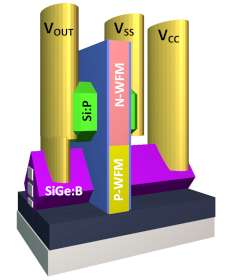

Het schema begint met het gebruik van wat algemeen wordt aangenomen als de transistorstructuur van de volgende generatie, genaamd nanosheet, nanoribbon, nanodraad of gate-all-around-apparaat, afhankelijk van wie erbij betrokken is. In plaats van dat het grootste deel van de transistor bestaat uit een verticale vin van silicium, zoals tegenwoordig het geval is, bestaat het kanaalgebied van de nanoplaat uit meerdere, horizontale, nanometer dunne vellen die op elkaar zijn gestapeld.

De ingenieurs van Intel gebruikten deze apparaten om het eenvoudigste CMOS-logische circuit, een omvormer, te bouwen. Het vereist twee transistors, twee stroomaansluitingen, een ingangsverbinding en een uitgang. Zelfs als de transistors naast elkaar zitten, zoals tegenwoordig, is de opstelling erg compact. Maar door de transistors op elkaar te stapelen en de onderlinge verbindingen aan te passen, werd de voetafdruk van de omvormer gehalveerd.

De omvormer bestaat uit twee transistors boven elkaar met een aantal gemeenschappelijke onderdelen en verbindingen.

De omvormer bestaat uit twee transistors boven elkaar met een aantal gemeenschappelijke onderdelen en verbindingen.

Het recept van Intel voor het bouwen van gestapelde nano-vellen wordt een zelfgericht proces genoemd, omdat het beide apparaten in wezen dezelfde stap bouwt. Dat is belangrijk omdat het toevoegen van een tweede stap – bijvoorbeeld door ze op afzonderlijke wafers te bouwen en de wafers vervolgens aan elkaar te binden – kan leiden tot verkeerde uitlijningen die mogelijke circuits zouden vernietigen.

In wezen is het proces een wijziging van de stappen die nodig zijn om nanosheet-transistors te maken. Het begint met herhaalde lagen silicium en siliciumgermanium. Dit wordt vervolgens gemodelleerd tot een hoge smalle vin en het siliciumgermanium wordt weggeëtst om een zwevende set silicium nanobladen achter te laten. Normaal gesproken zouden alle nanobladen een enkele transistor vormen. Maar hier zijn de bovenste twee nanobladen verbonden met met fosfor gedoteerd silicium om een NMOS-apparaat te vormen, en de onderste met met boor gedoteerd siliciumgermanium om PMOS op te leveren.

De volledige ‘integratiestroom’ is natuurlijk ingewikkelder, maar onderzoekers van Intel hebben er hard aan gewerkt om het zo eenvoudig mogelijk te houden, zegt Robert Chau, Intel senior fellow en directeur van componentenonderzoek. "De integratiestroom kan niet te ingewikkeld zijn, want dat heeft gevolgen voor de bruikbaarheid van het maken van chips met gestapelde CMOS. Dit is een heel praktische flow met respectabele resultaten."

"Als we het eenmaal onder de knie hebben, zal de volgende stap zijn om achter de voorstelling aan te gaan", zegt hij. Dat zal waarschijnlijk inhouden dat de PMOS-apparaten worden verbeterd, die momenteel achterlopen op de NMOS in hun vermogen om stroom te sturen. Het antwoord op dat probleem is waarschijnlijk de introductie van "spanning" op het transistorkanaal, zegt Chau. Het idee is om het rooster van het siliciumkristal zo te vervormen dat ladingsdragers (in dit geval gaten) sneller doorvliegen. Intel introduceerde spanning in zijn apparaten in 2002. In afzonderlijk onderzoek bij IEDM toonde Intel een methode om zowel drukspanning als trekspanning te produceren in nanoribbon-transistors.

Andere onderzoeksorganisaties streven ook naar gestapelde nanosheets-ontwerpen, hoewel ze soms complementaire FET’s of CFET’s worden genoemd. De Belgische onderzoeksorganisatie Imec was een pionier op het gebied van het CFET-concept en rapporteerde de constructie ervan op IEEE VLSI Symposia afgelopen juni. De Imec-componenten waren echter niet volledig gemaakt van nanosheet-transistors. In plaats daarvan bestond de onderste laag uit een FinFET en de bovenkant uit een enkele nanosheet. Onderzoekers in Taiwan rapporteerden de productie van een CFET-structuur met elk een enkele nanosheet voor de PMOS en NMOS. Het circuit van Intel had daarentegen een NMOS van twee nanosheets bovenop een PMOS van drie nanosheets, wat dichter ligt bij hoe apparaten er waarschijnlijk uit zullen zien tegen de tijd dat stapelen noodzakelijk wordt.